University of Houston researchers utilized nano-pantography to provide high-throughput, versatile, and large scale fabrication of nanometer-sized complex patterns over large surface areas by simultaneously focusing a broad ion beam with micro-electrostatic lenses on the substrate. When a wafer used in semiconductor manufacturing is tilted off normal (with respect to the ion beam axis), the focal point is laterally displaced, allowing the focused beams to be rastered, thus forming a desired pattern. The desired pattern can be replicated simultaneously in potentially millions of spots over tens of square centimeters.

The nano-pantography process can create nanodots and etching patterns on the surface of a substrate, and it allows for the creation of complex formations including, but not limited to nanowires, nanotubes, nanodevices and nanocircuits. Furthermore, the available surface area of the micro-lens array may be utilized to incorporate larger scale circuitry to address and control the formations, such as nanodevices and nanocircuits, created within the holes of the micro-lens.

Current focused ion beam techniques are capable of writing nanometer-sized features but are very slow. Existing methods for making small features consist of lithographically defining polymeric resist materials and then transferring the developed pattern into the desired underlying film or substrate by plasma etching.

State-of-the-art immersion lithography can produce features as small as 45 nm, but is complex and costly. Ion beam or electron beam proximity or projection lithography methods are capable of much finer resolution (e.g., features sized in the tens of nm), but require expensive and fragile masks. Some of the finest features may be made by electron beam writing into resist. While this method is very good for prototype devices, it is not practical for large-scale fabrication and production because the writing speed is much too slow to cover a several square centimeters chip size area in a reasonable time.

Another approach to making devices with nanometer sized features is to use self-assembled monolayers (SAMs). SAMs with micron sized feature can be delineated by lithography or stamping; while complex patterns with nanometer-size features can be fabricated with block copolymers. Unfortunately, SAMs are limited in terms of possible patterns and materials and are therefore unsuitable for large scale nanofabrication.

The University of Houston nano-pantograph circumvents the limitations of immersion lithography, SAMS, and current ion beam techniques and provides a method of fabricating 2-D or 3-D shape patterns in a wide variety of materials over large areas. It is a further object of the present invention to provide a method that is largely unaffected by vibrations, thermal expansion and other alignment problems that usually plague other nanofabrication methods. Furthermore, the available surface area of the micro-lens array may be utilized to incorporate larger scale circuitry to address and control the formations, such as nanodevices and nanocircuits, created within the holes of the micro-lens array.

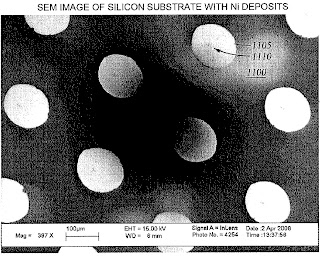

Figure SEM image of nano-deposits created using the system

The term nanometer-sized features means nano-scale features, e.g., features smaller than approximately 1 micron and at least approximately 1 nm. In certain applications, the nano-pantograph may be used to simultaneously form millions of identical nanometer-sized patterns. Nano-pantography can be used to etch patterns as well as to deposit patterned films at the nanometer scale with as much as a 100-fold reduction relative to the lens size. Certain embodiments of the nano-pantography method and system are generally capable of pattern resolutions of about 10 nanometers (nm). The nano-pantography system is capable of rapidly providing mass produced nano-patterning over a relatively large area such that the smallest lateral dimension of a feature may be as small as approximately 1 nm.

At step 210, an array of very small ion-focusing micro-lenses is fabricated on the substrate where the nanometer size features need to be etched or deposited. The micro-lenses are preferably electrostatic micro-lens. The substrate is then placed under vacuum on a stage that allows fine tuning of the sample position in space in three dimensions, at step 220. Next, at step 230, a broad area collimated beam of positive ions is extracted from a pulsed plasma and directed at the substrate. A positive voltage is applied to the top metal layer on the lens array at step 240. In response to the application of voltage, the ions are focused at the bottoms of the holes at step 250. The voltage on the micro-lenses may be optimized through experiments and simulations to allow the ions to focus at the correct distance. At the focal points, inert ions such as Ar.sup.+ can be made to cause rapid etching in the presence of reactive gas, at step 260, while metal ions sputtered from a target electrode can be extracted and deposited at energies below the sputtering threshold. As an example of the method illustrated in FIG. 2, simultaneous impingement of an Ar.sup.+ beam and a Cl.sub.2 effusive beam on an array of 950 nm diameter lenses can be used to etch 10 nm diameter features into a Si substrate, a reduction of 95 times.

At step 270, the substrate is tilted at desired angles to allow for parallel writing of multiple nanometer-sized patterns at substantially the same time. This embodiment of the invention is able to form multiple simultaneous nanometer-sized patterns, because, in part, the focal point of the ion beam is displaced when the ion beam axis is moved off normal with respect to the substrate. The line normal to the substrate intersects an imaginary horizontal plane at a selected distance from the substrate, e.g., a distance of about one meter from the substrate. As the wafer is tilted, the normal traces a pattern on the imaginary plane. Any pattern could be replicated by the ions that focus at the bottom of the holes, with a reduction by a factor of about 10.sup.6. In this manner, any desired pattern may be replicated by tilting the wafer at chosen angles and rastering the beam over the bottom of the holes, as shown at step 280. As a result, predetermined patterns can be formed simultaneously at the bottom of a large number of holes.

Given the flexibility of the present process of nano-pantography, a large number of nanometer-sized features may be produced on the substrate. For example, these features may range from simple patterns, such as nanodots, to complex formations including, but not limited to, nanowires, nanotubes, nanodevices and nanocircuits. Moreover, the present process of nano-pantography allows the user to select a wide variety of materials for the substrate and the nanometer-sized features. In addition, the method and system disclosed herein may be generally capable of rapidly providing mass produced nanometer sized features over a relatively large area such that the smallest lateral dimension of a feature may range in size from approximately 1 nm to approximately 50 nm.

The dead space between lenses is also available for large scale circuitry, which may be formed by conventional lithographic methods, to address and control discrete nano-devices or nano-circuits inside the holes. This is shown at step 290. In addition, because the lenses are mounted on the wafer, there is no need for the critical alignment and vibration control that is required for the alternative approach of projection of multiple focused ion beams onto a scanned substrate.

At step 270, the substrate is tilted at desired angles to allow for parallel writing of multiple nanometer-sized patterns at substantially the same time. This embodiment of the invention is able to form multiple simultaneous nanometer-sized patterns, because, in part, the focal point of the ion beam is displaced when the ion beam axis is moved off normal with respect to the substrate. The line normal to the substrate intersects an imaginary horizontal plane at a selected distance from the substrate, e.g., a distance of about one meter from the substrate. As the wafer is tilted, the normal traces a pattern on the imaginary plane. Any pattern could be replicated by the ions that focus at the bottom of the holes, with a reduction by a factor of about 10.sup.6. In this manner, any desired pattern may be replicated by tilting the wafer at chosen angles and rastering the beam over the bottom of the holes, as shown at step 280. As a result, predetermined patterns can be formed simultaneously at the bottom of a large number of holes.

Given the flexibility of the present process of nano-pantography, a large number of nanometer-sized features may be produced on the substrate. For example, these features may range from simple patterns, such as nanodots, to complex formations including, but not limited to, nanowires, nanotubes, nanodevices and nanocircuits. Moreover, the present process of nano-pantography allows the user to select a wide variety of materials for the substrate and the nanometer-sized features. In addition, the method and system disclosed herein may be generally capable of rapidly providing mass produced nanometer sized features over a relatively large area such that the smallest lateral dimension of a feature may range in size from approximately 1 nm to approximately 50 nm.

The dead space between lenses is also available for large scale circuitry, which may be formed by conventional lithographic methods, to address and control discrete nano-devices or nano-circuits inside the holes. This is shown at step 290. In addition, because the lenses are mounted on the wafer, there is no need for the critical alignment and vibration control that is required for the alternative approach of projection of multiple focused ion beams onto a scanned substrate.